Lola was designed as a simple, easily learnable hardware description language for describing synchronous, digital circuits. In addition to its use in a digital design course for second year computer science students at ETH Zürich, the Institute for Computer Systems uses it as a hardware description language for describing hardware designs in general and coprocessor applications in particular.

The purpose of Lola is to statically describe the structure and functionality of hardware components and of the connections between them. A Lola text is composed of declarations and statements. It describes the hardware on the gate level in the form of signal assignments. Signals are combined using operators and assigned to other signals. Signals and the respective assignments can be grouped together into types. An instance of a type is a hardware component. Types can be composed of instances of other types, thereby supporting a hierarchical design style and they can be generic (e.g. parametrizable with the word-width of a circuit).

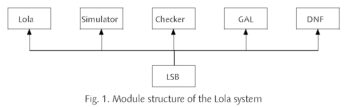

The Lola System is a toolbox consisting of various modules whose commands serve to specify, implement, and test digital circuits. These notes explain its structure to the user of Lola and to the implementer of additional tools. The system’s base is a module containing the definition of the central data structure used to describe digital circuits. Its name is LSB (Lola System Base). Typically, such a data structure is generated from a Lola text by the compiler, and thereafter used as argument for further processing steps, such as simplification, analysis, comparison, simulation, and layout generation. Fig. 1 gives an overview of the described components and their interdependence.

Lola-2: A Logic Description Language, Language description

Lola-2: Translating from Lola to Verilog

Tools for Digital Circuit Design using FPGAs

H Eberle and S. Gehring and S. Ludwig and N.Wirth, 1994

This collection of five papers describes concept and facilities of a system to aid in the design of digital circuits. It is being used in classes and laboratories for circuit design, and also for the development of prototype circuits in research projects. The collection comprises the report on the Lola language for specifying digital circuits, an introduction to field programmable gate arrays (FPGA) and the Atmel 6000 architecture, the user manual of the CL layout editor, the user manual of the CL design checker, and the description of two FPGA extension boards for Ceres-3.

A Laboratory for a Digital Design Course Using FPGAs

Stephan Gehring Stefan Ludwig Niklaus Wirth, 1994

In our digital design laboratory we have replaced the traditional wired circuit modules by workstations equipped with an extension board containing a single FPGA. This hardware is supplemented with a set of software tools consisting of a compiler for the circuit specification language Lola, a graphical layout editor for design entry, and a checker to verify conformity of a layout with its specification in Lola. The new laboratory has been used with considerable success in digital design courses for computer science students. Not only is this solution much cheaper than collections of modules to be wired, but it also allows for more substantial and challenging exercises.

Lola Compiler for Project Oberon, 2013 Edition

LSS.Mod

LSB.Mod

LSP.Mod

LSC.Mod

LSV.Mod

SmallPrograms.Lola

Lola Definition of RISC5 Computer

RISC5.Lola

LeftShifter.Lola

RightShifter.Lola

Multiplier.Lola

Divider.Lola

FPAdder.Lola

FPMultiplier.Lola

FPDivider.Lola

RISC5Top.Lola

PS2.Lola

MouseP.Lola

RS232R.Lola

RS232T.Lola

SPI.Lola

VID.Lola

DCMX3.v

FPGA-related Work

Hardware Design with Field Programmable Gate Arrays (FPGAs), 1990-1999

Similarity and difference between hardware and software design always had intreagued Wirth as a topic. With the emergence of programmable logic devices, the gap between the two fields narrowed. A project to familiarize a team with the new possibilities was established, and research in design methods using the new devices was started. It led to a set of design tools, including a specification language (Debora, B. Heeb), its compiler with several “back ends” for printed circuits boards, PLDs, and FPGAs. The usefulness of these tools was demonstrated by applying them in the construction of a workstation (Chamaeleon, also Ceres-3). The construction process starting from a textual specification and ending with a board layout and PLD programs was automated, and it required almost no manual intervention.

Wirth realized early, that FPGAs would be particularly useful as a field for experimentation in learning digital circuit design, replacing expensive, pluggable circuit modules by programmable cells. He equipped 25 Ceres-3 workstations in a student laboratory with an FPGA and uses them intensively in a digital design class. Along with a new project in tool design went the formulation of his language Lola, specifically tailored to the need of teaching in a systematic manner, dispensing with the myriads of side-issues inherent in commercial HDLs. The tool set consists of a compiler converting the program (circuit) text into an abstract data structure suitable for further processing, an editor for constructing circuits implemented by the FPGA, i.e. for generating a layout, and a checker comparing the specification in Lola with the layout.

The TRM: Experiments in Computer System Design

The Design of a RISC Architecture and its Implementation with an FPGA

– [RISC0.v]

– [RISC0Top.v]

– [PROM.v]

– [DRAM.v]

– [Multiplier.v]

– [Multiplier1.v]

– [Divider.v]

– [RISC0.ucf]

– [RS232R.v]

– [RS232T.v]

StandalonePrograms.Mod

RISC Architecture

Three Counters