Andrew S. Tanenbaum, Johan W. Stevenson and H. van Staveren

# Description of an Experimental machine Architecture for use with Block Structured Languages

Rapport nr. IR-54

# VRIJE UNIVERSITEIT AMSTERDAM

Wiskundig Seminarium, De Boelelaan 1081, 1081 HV Amsterdam

DESCRIPTION OF AN EXPERIMENTAL MACHINE ARCHITECTURE FOR USE WITH BLOCK STRUCTURED LANGUAGES

Andrew S. Tanenbaum Johan W. Stevenson Hans van Staveren

April 1980

Informatica Rapport IR-54

Abstract

EM-1 is a machine architecture designed to be interpreted on microcomputers. It has an instruction set convenient for compilers as well as a compact object program format. Furthermore, the encoding has been done to make interpretation with a cost penalty of roughly a factor of 5-8 feasible. This document describes the machine architecture, its instructions and their meanings.

# TABLE OF CONTENTS

| 1. INTRODUCTION                                      | 1  |

|------------------------------------------------------|----|

| 2. MEMORY                                            | 3  |

| 3. INSTRUCTION ADDRESS SPACE                         | 6  |

| 4. DATA ADDRESS SPACE                                | 7  |

| 5. MAPPING OF EM-1 MEMORY ONTO TARGET MACHINE MEMORY | 13 |

| 6. POSSIBLE SUCCESSORS TO EM-1                       | 18 |

| 7. DESCRIPTORS                                       | 20 |

| 8. INPUT/OUTPUT AND OTHER MONITOR CALLS              | 22 |

| 9. TRAPS AND INTERRUPTS                              | 24 |

| 10. EM-1 MACHINE LANGUAGE                            | 27 |

| 11. EM-1 ASSEMBLY LANGUAGE                           | 31 |

| 12. ASSEMBLY LANGUAGE INSTRUCTION LIST               | 36 |

| 13. KERNEL INSTRUCTION SET                           | 40 |

| APPENDIX 1. OFFICIAL EM-1 MACHINE DEFINITION         | 43 |

| APPENDIX 2. EM-1 CODE TABLES                         | 65 |

| APPENDIX 3. AN EXAMPLE PASCAL PROGRAM IN EM-1        | 71 |

#### 1. INTRODUCTION

$\mbox{EM-1}$  is an Experimental Machine architecture designed with the following goals in mind:

- A compact instruction set, to reduce the amount of memory needed ed for program storage, and to reduce the time needed to transmit programs over communication lines.

- The architecture should ease the task of code generation for high level languages such as Pascal, C, ADA, Algol 68, BCPL, etc.

- 3. It should be designed with microprogrammed implementations in mind; in particular, the use of many short fields within instruction opcodes should be avoided, since their extraction by the microprogram is inefficient.

- 4. The design should allow interpretation on, or translation to, a wide range of existing machines. Design decisions should be delayed as far as possible and the implications of these decisions should be localized as much as possible.

- It should be relatively easy to adapt the machine to new technological trends such as 32-bit address spaces or 32-bit machine words.

The basic architecture is based on the concept of a stack. The stack is used for procedure return addresses, actual parameters, local variables, and arithmetic operations. There are a small number of built-in object types, for example single and double precision integers, floating point numbers, pointers and sets of bits. There are instructions to push and pop objects to and from the stack. The push and pop instructions are not typed. They only care about the size of the objects. For each built-in type there are reverse Polish type instructions that pop two objects from the top of the stack, perform an operation on them, and push the result back onto the stack.

There are no visible general registers used for arithmetic operands etc. This is in contrast to most third generation computerw, which usually have 8 or 16 general registers. The decision not to have a group of general registers was fully intentional, and follows W.L. van der Poel's dictum that a machine should have 0, 1, or an infinite number of any feature. General registers have two primary uses: to hold intermediate results of complicated expressions, e.g.

$$\cdot ((a*b + c*d)/e + f*g/h) * i$$

and to hold local variables.

Various studies have shown that the average expression has fewer than two operands, making the former use of registers of doubtful value. The present trend toward structured programs consisting of many small procedures greatly reduces the value of registers to hold local variables because the large number of procedure calls implies a large overhead in saving and restoring the registers at every call.

Although there are no general purpose registers, there are a small number of internal registers with specific functions as follows:

PC: Program Counter. Byte number of next instruction

LB: Local Base. Points to zeroth local variable in the current procedure.

SP: Stack Pointer. Points to the highest occupied word on the stack.

HP: Heap Pointer. Points to the bottom of the heap area.

Furthermore, reverse Polish code is much easier to generate than multiregister machine code, especially if highly efficient code is desired. High performance can be achieved by keeping part of the stack in high speed storage (a cache or microprogram scratchpad memory) rather than in primary memory.

Again according to van der Poel's dictum, all EM-1 instructions have zero or one operand. We believe that instructions needing two operands can be split into two simpler ones. The simpler ones can probably be used in other circumstances as well. Moreover, these two instructions together often have a shorter encoding than the single instruction before.

This document describes the EM-1 machine at three different levels: the abstract level, the assembly language level and the machine language level. The most important level is that of the abstract EM-1 architecture. This level deals with the basic design issues. Only the functional capabilities of instructions are relevant, not their format or encoding. Most chapters of this document refer to the abstract level and it is explicitly stated whenever another levels is described. The assembly language is intended for the compiler writer. It presents a more or less orthogonal instruction set and provides symbolic names for data. Moreover, it facilitates the linking of separately compiled 'modules' into a single program by providing several pseudo instructions. The machine language is designed to make program text compact and to make decoding easy. The binary representation of the machine instruction set is far from orthogonal. Frequent instructions have a short opcode. The encoding is fully byte oriented. These bytes do not contain small bit fields, because bit fields would slow down decoding considerably. The encoding is nevertheless efficient: within 5% of the optimal Huffman code, measured over a large sample of Pascal programs.

A common use for EM-1 is for producing portable (cross) compilers. When used this way, the compilers produce EM-1 assembly language as their output. To run the compiled program on the target machine, another program, called 'back end', translates the EM-1 assembly language to the target machine's assembler. When this approach is used, the format of the EM-1 machine language instructions is irrelevant. On the other hand, when writing an interpreter for EM-1 machine language programs, the interpreter must deal with the machine language and not with the assembly language. This point is not trivial, because the semantics of many EM-1 assembly language instructions systematically differ from their machine language counterparts. For example, if an assembly language operand must be even, the machine language representation may not include the low order bit, which is always zero.

The machine described in this document, EM-1, uses machine words of 16 bits and pointers fitting in one machine word. There are two planned successors. One, called EM-2, uses two word pointers to address very large address spaces. The other successor, EM-3, has machine words of 32 bits. A single word is used for pointers in EM-3.

#### 2. MEMORY

The EM-1 machine has two distinct address spaces, one for instruction and one for data. Each address space is divided up into 8-bit bytes. Bytes are the smallest addressable units. Bytes are numbered consecutively from 0 to some maximum. For the EM-1 machine we have made the following choices:

DECISION A-1: The instruction address space consists of up to 2 \*\* 16 bytes. DECISION B-1: The data address space consists of up to 2 \*\* 16 bytes.

Therefore, all addresses can be represented in two bytes.

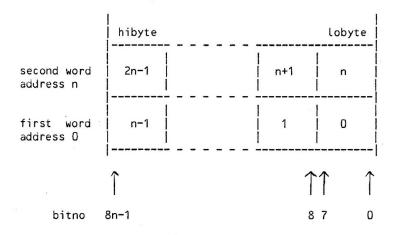

While bytes are the smallest addressable units, the basic unit in EM-1 is the machine word. The low order byte of a machine word is the rightmost byte, and has an address that is a multiple of the wordsize n. Figure 1 shows the first two words, with addresses 0 and n.

Fig. 1. byte-word addressing

The first word contains bytes  $0,1,\ldots,n-1$ ; the second word contains bytes  $n,n+1,\ldots,2n-1$  etc. Machine words are addressed by the address of the low order byte. For the EM-1 machine we have made the following choice:

DECISION C-1: A machine word consists of two bytes.

Thus all EM-1 words have even addresses.

The size of all objects in EM-1 is an integral number of words with one exception: objects consisting of a single byte. There are only two operations allowed on single byte objects: push it onto the stack and pop it from the stack. The addressing of bytes in memory is always indirect. If a single byte object is pushed onto the stack it is put in the low order byte of a word and the rest of the word is cleared to zero. Popping a byte from the stack removes a word from the stack, stores the low order byte of this word in memory and discards the rest of the word.

The assembly language format of instructions that reference memory by offset, requires the offset to be a multiple of the word size. For example, LOL 8 means fetch the local variable 8 bytes from the base of the current stack frame. To make compact encoding possible the offset actually present in the machine instructions is given in words, rather than in bytes. However, for simplicity, the offset specified in the assembly language is always in bytes. The compiler writer and the back end writer need not be aware of the details of the machine encoding.

The same remarks as for offsets apply to the size of objects. Sizes in assembly language are always in bytes and are one byte or a multiple of the wordsize. They are specified in words in the machine language and there is a special encoding for the size of one byte.

Some instructions fetch their offset or object size argument indirectly, for instance from the top of the stack. These offsets and sizes are always in bytes, so that the instruction itself must check that the addresses are word addresses or that the sizes are a single byte or word multiples.

The format of pointers into both address spaces is explicitly undefined. Each implementor of EM-1 may choose a suitable representation of pointers himself. The size of a pointer, however, is fixed, so that the compiler writer knows how much storage to allocate for a pointer. For EM-1 the size of pointers into the data address space as well as into the instruction address space is a single word.

A minor problem is raised by the undefined pointer format. Some languages, notably Pascal, require a special, otherwise illegal, pointer value to represent the nil pointer. The current Pascal-VU compiler uses the single precision integer value 0 as nil pointer. This value is also used by many C programs as normally impossible address. A better solution would be to have a special instruction loading an illegal pointer value, but it is hard to imagine an implementation for which the current solution is inadequate, especially since the first word in the EM-1 data space is special and probably not the target of any pointer.

The next two chapters describe the EM-1 memory in more detail. One describes the instruction address space, the other the data address space. Figure 2 gives an overview of these memory partitions.

A design goal of EM-1 has been to allow its implementation on a wide range of existing machines, not only designing a new one to be built in hardware. To this extent we have tried to minimize the demands of EM-1 on the memory structure of the target machine. Therefore, apart from the logical partitioning, EM-1 memory is divided into 'fragments'. A fragment consists of consecutive machine words and has a base address and a size. The only way to address the words of a fragment is by offsetting from its base address. The base address may only be used to address words of the corresponding fragment, i.e. offsets greater than the fragment's size are illegal.

It will be clear that fragments may be allocated anywhere in the address space and that only the calculation of the base address must be adapted. Reallocation of fragments at run time, however, is not trivial, because pointers to fragment words may be stored, which must then be relocated.

While following the logical partitioning in the next chapters, we will indicate the relation to fragments.

```

1.

Instruction address space

1.1.

Procedure descriptor table

1.1.1.

Number of bytes for parameters

1.1.2.

Procedure base address

1.1.x

1.2.

Program text

1.2.1.

Procedure text

2.

Data address space

2.1.

Global data area

2.1.1.

Global data blocks

2.1.1.1.

ABS block

Line number

2.1.1.1.1.

2.1.1.1.x.

2.1.1.2.

CON blocks

2.1.1.3.

ROM blocks

2.1.1.4.

BSS blocks

2.1.1.5.

HOL blocks

2.1.2.

Local data area

2.1.2.1.

Procedure frame

2.1.2.1.1.

Mark block zone

2.1.2.1.1.1.

Static link

2.1.2.1.1.2.

Dynamic link

2.1.2.1.1.3.

Return address

2.1.2.1.1.x.

......

2.1.2.1.2.

Actual parameter zone

2.1.2.1.3.

Local variable zone

2.1.2.1.4.

Dynamic local generator zone

2.1.2.2.

Stack

2.1.3.

Heap data area

```

Fig. 2. Memory overview.

#### 3. INSTRUCTION ADDRESS SPACE

The instruction space of the EM-1 machine contains the procedure descriptor table and the binary machine code for procedures. The instruction space does not change during the execution of a program, so that it may be protected.

The procedure descriptor table contains an entry for each procedure in the program. The size of a descriptor is explicitly undefined. A descriptor must contain at least two items:

- 1. A constant telling how many bytes of parameters the procedure has.

- The base address of the procedure's code. This is the only place that procedure addresses are used.

A descriptor may contain other (implementation dependent) information for debugging or monitoring. The most important reason to have a procedure descriptor table is that it makes very compact procedure calls possible. It may not be necessary for some implementations, however, to have a procedure descriptor table at all.

Each procedure has a single entry point: the first instruction, located at the base address stored in the descriptor. There is a single EM-1 program counter PC pointing to the next instruction to be executed. The procedure pointed into by PC is called the 'current' procedure. A procedure may call another procedure using the CAL or CAS instruction. The calling procedure remains 'active' and is resumed whenever the called procedure returns. Note that a procedure may have many 'active' invocations.

Each procedure must return properly. It is not allowed to fall through to the code of the next procedure. There are several ways to exit from a procedure:

- the HLT instruction that stops the program, exiting all active procedures.

- the RET or RES instruction, which returns to the calling procedure.

- the RTT instruction, which exits a trap handling routine and resumes the trapping instruction (see below).

- a non-local jump using the CSA or CSB instructions. These instructions are normally used for case statements to jump to selected pieces of code local to the procedure that executes them. If these instructions must be used to exit from procedures you have to proceed with great care, because you have to unravel the stack yourself! This way of exiting a procedure should only be used in emergencies.

All branch instructions are relative to the program counter. There is only one branch instruction that jumps backward: BRB, unconditional branch backward. Branch instructions can never jump out of a procedure. Because the operand of a branch instruction must have a fixed range accommodating all possible offsets, there must be a maximum procedure size:

DECISION D-1: The code for a single procedure must fit in 2 \*\* 15 bytes.

The program text for each procedure, as well as the descriptor table, are fragments and can be allocated anywhere in the instruction address space.

#### 4. DATA ADDRESS SPACE

The data address space is divided into three parts, called 'areas', each with its own unique addressing method: global data area, local data area (including the stack), and heap data area. These data areas must be part of the same address space because all data is accessed by the same type of pointers. However, constructing pointers is different for these data areas.

Global data is allocated by using several pseudo instructions in the assembly language, as described below. The size of the global data area is fixed per program. Global data is addressed absolutely in the machine language. Many instructions are available to address global data. They all have an absolute address as operand. Examples are LOE, LAE and STE. The operands of these instructions range from 0 to some maximum.

DECISION E-1: The maximum size of global data is 2 \*\* 15 bytes

Part of the global data area is initialized by the compiler, part of it is initialized with program arguments supplied by the user and the rest is not initialized at all or is initialized with some arbitrary value, typically -32768 or O. Part of the initialized global data may be made read-only if the implementation supports protection.

The local data area contains the stack and some data for each active procedure invocation, called a 'frame'. The size of the local data area varies. The base address is fixed, so it grows from a low EM-1 address to a high EM-1 address. On top of the current procedure frame resides the operand stack. The stack pointer SP always points to the top of the stack and it thereby marks the high end of the local data area. Local data is addressed by offsetting from the local base pointer LB. LB always points to the frame of the current procedure. Only the words of the current frame can be addressed directly. Variables in other active procedures are addressed by following the chain of statically enclosing procedures using the LEX instruction. Many instructions have offsets to LB as argument, for instance LOL, LAL and STL. The argument of these instructions range from 0 to some maximum.

DECISION F-1: The maximum size of a procedure frame including the operand stack is 2 \*\* 15 bytes.

The procedure call instructions CAL and CAS transform some words on top of the stack into a new frame. Each procedure, therefore, starts with an empty stack. The return instructions RET, RES and RTT remove a frame. RET and RES may copy some words on top of the stack of the returning procedure to the top of the stack of the previous routine, as result value.

The heap data area grows downwards. It is initially empty. The initial value of the heap pointer HP marks the high end. The heap pointer may be manipulated by the LOR and STR instructions. The heap can only be addressed indirectly, by pointers obtained from previous values of HP.

#### 4.1. GLOBAL DATA AREA

The size of global data is fixed at compile time. Global data is allocated by several pseudo instructions in the EM-1 assembly language. This section anticipates the description of the assembly language below, but the concepts are similar to other assembly languages. Each pseudo instruction allocates some words. The words allocated for a single pseudo form a 'block'. A block differs from a fragment, because, under certain conditions, several blocks are allocated in a single fragment. This guarantees that the words of these blocks are consecutive.

Initialized global data is allocated by the pseudo instruction CON. It needs at least one operand. There are several operand types: single and double precision integer constants, floating point constants, procedure numbers, instruction labels, addresses in the global data area and strings. Strings are byte sequences. For each operand an integral number of words, determined by the operand type, is allocated and initialized. The assembler pads strings out to an integral number of words.

The pseudo instruction ROM is the same as CON, except that it guarantees that the initialized words will not change during the execution of the program. This information allows optimizers to perform certain calculations such as array indexing and subrange checking at compile time instead of at run time.

The pseudo instruction BSS allocates uninitialized global data. The only operand to this pseudo is the number of bytes required, which must be a multiple of the wordsize. All words of a BSS block may have different initial values, but most implementations will assign some fixed value to these words, typically -32768 or 0.

Global data is addressed absolutely in binary machine language. Most compilers, however, cannot assign absolute addresses to their global variables, especially not if the language allows programs to be composed of several separately compiled modules. The assembly language therefore allows the compiler to name global data blocks by prepending CON, ROM and BSS pseudos with alphanumeric labels. Moreover, the only way to address these named global data blocks is by using their name. It is the task of the assembler/loader to translate these labels into absolute addresses. These labels may also be used in CON and ROM pseudo instructions to initialize pointers.

Unlike many other assembly languages, the EM-1 assembly language requires all operands of normal and pseudo instructions to be either a number or an identifier, but not an expression. This makes it impossible to address the third word of a ten word BSS block directly. Thus LOE LABEL+4 is not permitted, nor is CON LABEL+4. To access LABEL+4 you must first load the base address of the BSS block using its name (LABEL). Then a second instruction may add an offset (4) to this address and can load the addressed object onto the stack. This restriction, although annoying, is fully intentional, and greatly aids optimization.

The pseudo instruction HOL offers a partial solution to this problem. HOL is similar to BSS in that it requests an uninitialized global data block with size equal to the value of its operand (in bytes, but a multiple of the word-size). Addressing of a HOL block, however, is quasi absolute. The first word is addressed by 0, the second word by 2 etc. in assembly language. The

assembler/loader adds the base address of the HOL block to these numbers to obtain the absolute address in the machine language.

The scope of a HOL block starts at the HOL pseudo and ends at the next HOL pseudo or at the end of a module (EOF pseudo) whatever comes first. Each instruction falls in the scope of at most one HOL block, the current HOL block.

A fifth type of global data is a small block, called ABS block, with implementation defined size. It is addressed absolutely, both in assembly language and in the machine language. The first word has address 0 and is used to maintain the source line number. Special instructions LIN and LNI are provided to update this counter. Other items in this block might be the arguments supplied by the caller of this program.

Note that all numeric operands of the instructions that address the global data area refer to the current HOL block if they are preceded by at least one HOL pseudo in the same module and that they refer to the ABS block otherwise. Thus LOE O loads the zeroth word in the most recent HOL, unless no HOL has appeared in the current file, in which case it loads the zeroth word in the ABS fragment.

The global data area is highly fragmented. The ABS block and each HOL block form a separate fragment. The situation for CON, ROM and BSS blocks is more complex. The assembler groups several blocks into a single fragment. A fragment only contains blocks of the same type: CON, ROM or BSS. It is guaranteed that the words allocated for two CON pseudos are allocated consecutively in a single fragment, unless these CON pseudos are separated in the assembly language program by one or more of the following pseudos:

ROM, BSS, HOL, END and EOF

A similar statement can be made for ROM pseudos and for BSS pseudos.

#### 4.2. LOCAL DATA AREA

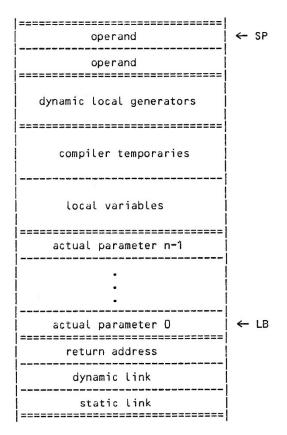

The local data area consists of a sequence of frames, one for each active procedure. On top of the frame of the current procedure resides the stack. Frames are generated by procedure calls and are removed by procedure returns. A procedure frame consists of 5 'zones':

- 1. The mark block.

- 2. The actual parameters

- 3. The local variables and compiler temporaries

- 4. The dynamic local generators

- 5. The operand stack.

A sample frame is shown in Fig. 3.

The first step in the procedure calling sequence is to deposit a mark block on the stack of the current procedure (using the MRK or MRS instruction). The mark block contains at least the following items:

- static link: the LB value of the most recent invocation of the statically enclosing procedure. This field supports the linkage needed by block structured languages.

- dynamic link: the LB value of the calling procedure.

- return address of the calling procedure, pointing into the instruction space.

The exact format and encoding of the mark block is explicitly undefined and may vary from implementation to implementation, i.e. it is up to the implementor to decide the number of machine words, their order and their encoding.

The second step in the calling sequence is to push the actual parameters on top of the stack of the calling procedure. The exact details are compiler dependent. If a procedure has no parameters this zone will be empty. Note that the evaluation of the actual parameters may imply the calling of procedures.

The third and last step is to call the procedure using the CAL or CAS instruction. Several tasks are performed by the call instructions. First, the LB is changed to point to the first word above the mark block, containing the first parameter if present. The new LB is calculated by subtracting the number of bytes passed as parameter (see procedure descriptor) from the stack pointer SP. Second, the old program counter PC is saved in the mark block, some words below the new LB. Third, the new program counter is fetched from the procedure descriptor and stored in PC.

Normally the first instruction of the called procedure will be BEG to advance SP, reserving space for local variables and compiler temporaries. The initial value of the allocated words is not defined, but implementations that check for undefined values will probably initialize them with the special 'undefined' pattern, typically -32768. This same instruction BEG may also be used to remove some words from the stack.

There is a version of BEG, called BES, which fetches the number of bytes to allocate from the stack. It can be used to allocate space for local objects whose size is unknown at compile time, so called dynamic local generators. By allocating the objects of known size first, these can be addressed using the more efficient instructions with fixed offset.

The distinction between the last four zones of procedure frames is rather vague. The only restriction is that SP may not be smaller than LB and that only words between LB and SP may be accessed by offsetting to LB.

It should be noted that procedures with a variable number of parameters cannot be accommodated. Each such procedure must have some maximum number of bytes worth of parameters, and exactly this number must be passed on each call. Of course the programmer or compiler is free to use the BEG instruction in the calling procedure to advance the stack pointer, thus simulating the passing of many dummy parameters in one instruction.

Each procedure frame is a separate fragment. Since any fragment may be placed anywhere in memory, procedure frames need not be contiguous. If for some reason it is necessary to implement frames non-contiguously, the call in-

struction must copy the mark block and actual parameters to the location of the new frame. However, this movement implies that an actual parameter that points to another actual parameter in the same fragment has to be relocated, an impossible task. Consequently, on implementations that do not store procedure frames contiguously, programs must not allow actual parameters to point to other actual parameters in the same procedure. It is difficult, however, to construct an example for which this restriction is prohibitive.

Fig. 3. A sample procedure frame.

# 4.3. HEAP DATA AREA

The heap area starts empty, with HP pointing to the high end of it. HP always contains a word address. The current value of HP can always be obtained by the LOR instruction. (Note: we use 'value' to indicate the byte number in the data space, independent of the pointer representation). A new value may be

stored in the heap pointer using the STR instruction. If the new value is smaller than the old one, then the heap grows downwards. If it is greater, then the heap shrinks. The value of HP may never exceed the original value of HP. All words between the current HP and the original HP are allocated to the heap. The heap may not grow into a part of memory that is already allocated for local or global data. If this is attempted the STR instruction will cause a trap to occur.

The only way to address the heap is indirectly. Whenever an object is allocated by decreasing HP, then the new HP value must be saved and can be used later on to address the allocated object. If, in the meantime, HP is increased so that the object is no longer part of the heap, then an attempt to access the object is not allowed. More strongly, if the heap pointer is decreased again to below the object address, then access to the old object gives undefined results.

The heap is a single fragment. All words have consecutive addresses. There are no limits on the size of the heap as long as it fits in the data address space.

# 5. MAPPING OF EM-1 MEMORY ONTO TARGET MACHINE MEMORY

The EM-1 architecture is designed to be implemented on a large number of existing and future machines. EM-1 memory is highly fragmented to make adaptation to various memory architectures possible. Format and encoding of pointers is explicitly undefined. Byte addressing is concentrated in a few instructions.

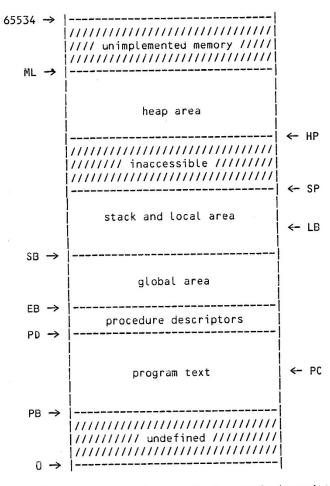

This chapter gives solutions to some of the anticipated problems. First we describe a possible memory layout for machines with 64k bytes of address space. The most straightforward layout is shown in figure 4.

Fig. 4. Memory layout showing typical register positions during execution of an EM-1 program.

Several target machine registers are used as base registers for the various memory pieces.

PD: points to the base of the procedure descriptor table.

PB: points to the base of the instruction address space.

EB: points to the base of the data address space.

SB: points to the base of the local data area.

ML: marks the high end of the addressable data space.

The stack grows from low EM-1 addresses to high EM-1 addresses, and the heap the other way. The memory between SP and HP is not accessible, but may be allocated later to the stack or the heap if needed. The local data area is allocated starting at the high end of the global data area.

Since EM-1 address 0 is not mapped onto target address 0, a problem arises when pointers are used. If a program pushed a constant, say 6, onto the stack, and then tried to indirect through it, the wrong word would be fetched, since EM-1 address 6 is mapped onto target address EB+6 and not target address 6 itself. This particular problem is solved by explicitly declaring the format of a pointer to be undefined, so that using a constant as a pointer is completely illegal. However the general problem of mapping pointers still exists.

There are two possible solutions. In the first solution EM-1 pointers are represented in the target machine as true EM-1 addresses, e.g. a pointer to EM-1 address 6 really is stored as a 6 in the target machine. This solution implies that every time a pointer is fetched EB must be added to it before it is used to reference the target machine's memory. If the target machine has powerful indexing facilities, EB can be kept in a target machine register, and the relocation can indeed be done on every reference to the data address space at a modest cost in speed.

The other solution consists of having EM-1 pointers refer to the true target machine address. Thus the instruction LAE 6 (Load Address of External 6) would push the value of EB+6 onto the stack. When this approach is chosen, back ends must know the value of EB, to translate all instructions that manipulate EM-1 addresses. However, the problem is not completely solved, since a compiler may have to initialize a pointer in CON or ROM data to point to a global address. This pointer must also be relocated by the back end or the interpreter.

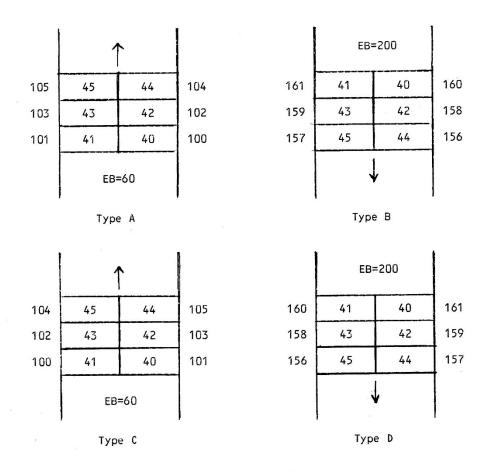

EM-1 requires the stack to grow from low to high EM-1 addresses. Some machines, however, have hardware PUSH and POP instructions that require the stack to grow downwards. If reasons of efficiency urge you to use these instructions, then the implementation of EM-1 may be done by implementing the memory layout shown in figure 4 upside down. This is possible because the pointer format is explicitly undefined. The first element of a word array will have a higher physical address than the second element. Problems arise for byte addressing, since even numbered bytes are still the low order bytes in a word and since words are still addressed by these low order bytes. The problem is demonstrated clearly in figure 5, type B: the bytes in a byte array allocated at EM-1 address 40 have non-linear physical addresses.

Figure 5. Four possible memory implementations. Numbers within the boxes are EM-1 addresses. The other numbers are physical addresses.

A similar problem may arise if EM-1 is implemented on machines for which the lowest addressed byte in a word is the high order byte, i.e. byte 0 is to the left of byte 1, instead of to the right. There are no problems with word addressing, because word addresses are still even. But byte addressing is difficult again. A fourth possible combination is to implement the EM-1 address space upside down on a machine with the bytes in a word swapped.

So, these two characteristics of the target machine - stack grows upwards or downwards, and the lowest addressed byte is the least significant byte (lsb) or the most significant byte (msb) - lead to four different EM-1 memory implementations:

A - stack upwards and lsb has lowest address

B - stack downwards and lsb has lowest address

C - stack upwards and msb has lowest address

# D - stack downwards and msb has lowest address

For each of these four possibilities we give the translation of the EM-1 instructions to push the third byte of a global data block starting at EM-1 address 40 onto the stack. The target machine used is a PDP-11 augmented with push and pop instructions. Registers 'r0' and 'r1' are used and suffer from sign extension for byte transfers. Push \$40 means push the constant 40, not word 40.

The translation of the EM-1 instructions depends on the pointer representation used. For each of the two solutions explained above the translation is given. The second solution, a true target machine address as pointer representation, needs to be modified slightly to obtain continuous addresses for contiguous bytes. Pointers to words are true target machine addresses, but pointers to bytes may be off by two.

First the translation for the four implementations using EM-1 addresses as pointer representation:

| EM−1 t                | type A                                  | type               | В                                    | type               | С                  | type               | D                  |

|-----------------------|-----------------------------------------|--------------------|--------------------------------------|--------------------|--------------------|--------------------|--------------------|

| LAE 40 p              | oush \$40                               | push               | \$40                                 | push               | \$40               | push               | \$40               |

| ā                     | oop r0<br>add \$3,r<br>oush r0          | pop<br>odd<br>push | r0<br>\$3,r0<br>r0                   | pop<br>add<br>push | r0<br>\$3,r0<br>r0 | pop<br>add<br>push | r0<br>\$3,r0<br>r0 |

| -<br>-<br>-<br>c<br>b | oop r0<br>-<br>-<br>clr r1<br>oisb eb(r |                    | r0<br>r0<br>s1,r0<br>r1<br>eb(r0),r1 | clr                | eb(r0),r1          | inc<br>-<br>clr    | eb(r0),r1          |

The translation for the four implementations, if the target machine address is used as pointer representation, is:

| EM-1   | type A                                           | type B                                               | type C                                                         | type D                                                     |

|--------|--------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|

| LAE 40 | push \$eb+40                                     | push \$eb-40                                         | push \$eb+40                                                   | push \$eb-40                                               |

| ADI 3  | pop r0<br>add \$3,r0<br>push r0                  | sub \$3,r0                                           | pop r0<br>add \$3,r0<br>push r0                                | pop r0<br>sub \$3,r0<br>push r0                            |

| LOI 1  | pop r0<br>-<br>clr r1<br>bisb (r0),r1<br>push r1 | pop r0 inc r0 xor \$1,r0 clr r1 bisb (r0),r1 push r1 | pop r0<br>-<br>xor \$1,r0<br>clr r1<br>bisb (r0),r1<br>push r1 | pop r0<br>inc r0<br>-<br>clr r1<br>bisb (r0),r1<br>push r1 |

The translation presented above is not intended to be optimal. Most machines can handle these simple cases in one or two instructions. It demonstrates, however, the flexibility of the EM-1 design. The number of EM-1 instructions that is influenced by the peculiar byte addressing is limited. It only affects:

LOI/LOS, STI/STS, LAR/LAS, SAR/SAS, LAI and SAI

If EM-1 is implemented on machines with address spaces larger than 64k bytes, then there are several possibilities to use this. The simplest one is to allocate instruction and data space each in a separate 64k piece of memory. EM-1 pointers must be represented in the target machine as true EM-1 addresses, because they must fit in a single machine word. The base registers PB and EB may be loaded in hardware registers wider than 16 bits, if available.

The next possibility is to have a 32-bit instruction address space and a 16-bit data address space. The only change to the basic machine needed to achieve this is to use two word addresses within the procedure descriptors and the mark blocks and perhaps for PC. Since the size of a procedure descriptor and the size of a mark block are explicitly undefined, this change is trivial. Changing from a 16-bit to a 32-bit instruction address space does not affect existing compilers. Assemblers and back ends for the various target machines will need only minor modifications in the following instructions:

MRK/MRS, CAL/CAS, RET/RES, CSA, CSB, TRP and RTT

Therefore, the machine with enlarged instruction space is still classified as EM-1, although one of the basic design decisions (A-1) is modified. It should be pointed out, however, that 64k of program space is sufficient for rather large programs.

A third possible implementation on machines with large address spaces is described in the next chapter.

#### 6. POSSIBLE SUCCESSORS TO EM-1

#### 6.1. EM-2

To use the large address space available on some machines effectively, the data address space of EM-1 should be increased. The main difficulty with increasing the data space is the need for larger (multiword) addresses in many contexts. There is no technical difficulty in changing the addresses from one to two words, but the effect is to increase program size and decrease program speed considerably.

We refer to the design with 32-bit pointers for both instruction and data space as EM-2. Actually, the choice of 16 or 32 bits can be made independently for instruction space and data space, but since the price of a 32 bit instruction space is rarely more than a few hundred words in the object program, and the price of a larger data space is considerable, a large data space and a small instruction space makes little sense. The list of decisions for the EM-2 design is slightly different:

DECISION A-2: The instruction address space consists of up to 2 \*\* 32 bytes.

DECISION B-2: The data address space consists of up to 2 \*\* 32 bytes.

DECISION C-2: A machine word consists of two bytes.

DECISION D-2: The code for a single procedure must fit in 2 \*\* 15 bytes.

DECISION E-2: The maximum size of global data is 2 \*\* 15 bytes

DECISION F-2: The maximum size of a procedure frame including the operand stack is 2 \*\* 15 bytes.

Compilers must be changed to reserve 2 words for pointer variables (the Pascal-VU compiler has such an option already built in). Assemblers, interpreters and back ends have to be changed as well, especially for the instructions that manipulate data addresses. But, using 32-bit pointers, several alternatives are available. The simplest one is to assign a 32k memory piece to the local and global data area each. Because of the unrestricted size of the heap, the rest of the address space can be allocated to heap objects.

A second alternative is to allow each fragment in the local area to occupy up to 32k bytes. The consequences for procedure calls of this approach are described above. The local and heap area compete for memory as before, the local area growing upwards and the heap growing in the opposite direction.

Allocating 32k to each fragment in global data is not straightforward, because each word in global data must be addressable by the 15-bit offsets to the instructions like LAE. If the 32-bit address space is divided into 65536 segments, each of 64k bytes, then one can use one of these segments for the normal global data and allocate large arrays in other segments. Each word in the address space can be addressed by loading the segment base address, using the new instruction LSA, and by adding an offset to this pointer using instructions like ADI.

## 6.2. EM-3

Both EM-1 and EM-2 use machine words of 16 bits. The same instruction set, however, can be used for a machine, EM-3, with 32-bit machine words. Addresses into the large address spaces fit into a single word again. The design decisions for EM-3 are:

DECISION A-3: The instruction address space consists of up to 2 \*\* 32 bytes.

DECISION B-3: The data address space consists of up to 2 \*\* 32 bytes.

DECISION C-3: A machine word consists of four bytes.

DECISION D-3: The code for a single procedure must fit in 2 \*\* 31 bytes.

DECISION E-3: The maximum size of global data is 2 \*\* 31 bytes DECISION F-3: The maximum size of a procedure frame including the operand stack is 2 \*\* 31 bytes.

Although the instruction set is the same as for EM-1, all compilers, optimizers, back end compilers, assemblers and interpreters have to be changed, as well as the compact assembly format and the binary machine encoding.

## 7. DESCRIPTORS

Besides the procedure descriptors used by the call instruction, several other instructions use descriptors, notably the range check instruction, the array instructions and the case jump instructions. Procedure descriptors are allocated in instruction space, the others in data space. The descriptors in data space may be constructed at run time, but more often they are fixed and allocated in ROM data.

Range check descriptors consist of two words:

- 1. lower bound

- 2. upper bound

The range check instruction checks a word on the stack against these bounds and causes a trap if the value is outside the interval. The value itself is neither changed nor removed from the stack.

Array descriptors describe a single dimension. For multi-dimensional arrays several array instructions in row are needed to access a single element. Array descriptors contain the following three words:

- 1. lower bound

- 2. upper bound lower bound

- 3. number of bytes per element

The array instructions LAR, SAR and AAR have the offset of the start of the descriptor from the base of the global data area as operand. The array instructions LAS, SAS and AAS fetch the pointer to the descriptor from the top of the stack.

The element A[I] is fetched as follows:

- a) Stack the address of A (e.g. using LAE, LEX, or LAL)

- b) Stack the value of I (16 bit integer)

- c) LAR n (n is offset for descriptor)

All array instructions pop the index and subtract the lower bound from it. If the result is negative, a trap occurs. If zero or positive, it is compared to upper bound - lower bound (the second descriptor word). If it is out of range, a trap occurs. If ok, (I - lower bound) is multiplied by the number of bytes per element (the third word). The result is added to the address of A, which replaces A on the stack.

At this point LAR (LAS), SAR (SAS) and AAR (AAS) diverge. AAR is finished. LAR pops the address and fetches the data item the size being specified by the descriptor (this must be a multiple of the word size, except for one byte); SAR pops the address and stores the data item now exposed.

The case jump instructions CSA and CSB both provide multiway branches within a single procedure (most likely the current one), selected by a case index. Both fetch two arguments from the stack: first a pointer to the case descriptor and then the case index. CSA uses the case index as index in the descriptor table, but CSB searches the table for an occurrence of the case index. Therefore, the descriptors for CSA and CSB, as shown in figure 6, are

different.

CSA selects the new PC by indexing. The lower bound is subtracted from the case index. If the result is greater or equal to 0 and less or equal to upper-lower, then fetch the offset from the list of offsets by indexing with index-lower. If index-lower is out of bounds or if the fetched offset is -1, then fetch the default offset. If the resulting offset is -1, then trap. If not, then calculate the new PC by adding the offset to the base of the procedure text mentioned in the procedure descriptor corresponding with the procedure number. By adding the offset to the procedure base you may not come in a different procedure.

CSB selects the new PC by searching. The table is searched for an entry with index value equal to the case index. The code offset of that entry (the default offset if no such entry found) is used to calculate the new PC as for CSA.

The choice of which case instruction to use for each source language case statement is up to the compiler. If the range of the index value is dense, i.e

(highest value - lowest value) / number of cases

is less than some threshold, then CSA is the obvious choice. If the range is sparse, CSB is better.

| offset of upb    | offset n-1        |

|------------------|-------------------|

| -                | index n-1         |

|                  |                   |

|                  | :                 |

| •                | offset 1          |

| offset of lwb+1  | index 1           |

| offset of lwb    | offset O          |

| upper - lower    | index 0           |

| lower bound      | number of entries |

| default offset   | default offset    |

| procedure number | procedure number  |

| CSA descriptor   | CSB descriptor    |

Figure 6. Descriptor layout for CSA and CSB

#### 8. INPUT/OUTPUT AND OTHER MONITOR CALLS

EM-1 differs from most conventional machines in that it has high level i/o instructions. Typical instructions are OPEN FILE and READ FROM FILE rather than low level instructions such as setting and clearing bits in device registers. By providing such high level i/o primitives, the task of implementing EM-1 on various non EM-1 machines is made considerably easier.

I/O is initiated by the MON instruction, which expects an iocode on top of the stack. Often there are also parameters p1,p2,...,pn which have been previously stacked in the order listed. Some i/o functions also provide results, which are returned on the stack. The table below lists the i/o codes and their results. This list is similar to the system calls of the UNIX operating system. (UNIX is a Trademark of Bell Laboratories.)

To execute a monitor call, proceed as follows:

- a) Stack the parameters in the order specified, one word per parameter

- b) Push the monitor call number (iocode) onto the stack

- c) Execute the MON instruction

The result of the MON instruction can be at most 3 words: e, R1, R0. Next to the number of each call in the list below, a three character code is given. If the call returns an error code (e), the first character of the code is e, else -. The next two characters tell whether return values R1 and R0 are present (digit) or absent (-). The order in which these return values are pushed onto the stack is: R0, R1, e. So the error code, if present, is found on top of the stack. If an error occurs on a monitor call having R0, R0 is also set to the error code.

List of monitor calls.

18 e--

2 e10 Fork() - spawn new process RO = processid of other process, R1=1 for child, O for parent Read(bufaddr,nbytes,fildes) - read from file RO = number of bytes actually read e-O Write(bufaddr,nbytes,fildes) - write on a file RO = number of bytes actually written (should be equal to nbytes) Open(string, open flag) - open for reading or writing or both RO = fildes Close(fildes) - close a file e10 Wait() - wait for process to terminate RO = process id , R1 = exit status 8 e-0 Creat(string, mode) - create a new file R0 = fildesLink(string1,string2) - link to a file 10 e-- Unlink(string) - remove directory entry 12 e-- Chdir(string) - change default directory 13 -10 Time() - get date and time RO = high order word, R1 = low order word 14 e-- Mknod(string,mode,addr) - make a directory or a special file 15 e-- Chmod(string, mode) - change mode of file 16 e-- Chown(string,owner,group) - change owner and group of a file

Stat(string, statbuf) - get file status

19 e10 Lseek(highword,lowword,fildes) - move read/write pointer

```

RO = prev. highword, R1 = prev. lowword

Getpid() - get process identification

20

RO = process id

Mount(string1,string2,rwflag) - mount file system

21

e--

22

e--

Umount(string) - unmount file system

Setuid(userid) - set user ID

e--

23

Getuid() - get user ID

24

-10

RO = real user ID , R1 = effective user ID

Stime(hightime, lowtime) - set time and date

Ptrace(pid,addr,request,data) - process trace

RO = returned value

Alarm(seconds) - schedule signal after specified time

27

--0

RO = previous value

Fstat(statbuf, fildes) - get file status

28

e--

29

Pause() - stop until signal

30 e--

Utime(string, timep) - set file times

Access(string, mode) - determine accessibility of file

33

e--

Nice(incr) - set program priority

Ftime(bufp) - get date and time

34

---

35

Sync() - update superblock

36

Kill(sig,pid) - send signal to a process

37

e--

e-O Dup(fildes, newfildes) - duplicate an open file descriptor

RO = new file descriptor

e10 Pipe() - create an interprocess channel

42

RO = read descriptor , R1 = write descriptor

43

Times(buffer) - get process times

Profil(buff,bufsiz,offset,scale) - execution time profile

44

Setgid(gid) - set group ID

46 e--

47

-10 Getgid() - get group ID

RO = real group ID , R1 = effective group ID

Sigtrp(trapno, signo) - see below

48

RO = previous value

Acct(file) - turn accounting on or off

51

e--

Phys(segreg, size, physadr) - allow a process to access phys. addr.

52

e--

Lock(flag) - lock a process in primary memory

53

e--

Ioctl(fildes,request,argp) - control device

54

Mpxcall(cmd, vec) - manipulate multiplexed files

56 e--

59 e-- Exece(name, argv, envp) - execute a file

60 e-- Umask(complmode) - set file creation mode mask

61 e-- Chroot(string) - change root directory

```

Codes 0, 1, 11, 17, 31, 32, 38, 39, 40, 45, 49, 50, 55, 57, 58, 62, and 63 are not used.

• The sigtrp() entry works specially. Normally, trapno is in the range 0 to 255. In that case it requests that signal signo will cause trap trapno to occur. When given trap number -2, default signal handling is reset, and when given trap number -3, the signal is ignored.

All of the above monitor calls, except for the sigtrp(), which is slightly modified, are the same as the UNIX version 7 system calls.

#### 9. TRAPS AND INTERRUPTS

EM-1 provides a means for the user program to catch all errors generated by the program itself, the hardware, or external conditions. This mechanism uses three instructions: SIG, TRP and RTT. This section of the manual may be omitted on the first reading since it presupposes knowledge of the EM-1 instruction set.

The SIG instruction expects a procedure identifier on the stack, that is a static link and a procedure number. From that moment on all errors will be passed to this procedure. When an error occurs, this procedure is called with the number of the error as the only parameter (see below). SIG returns an analogous procedure identifier on the stack representing the previous procedure for dealing with errors. Two consecutive SIGs are a no-op. After the procedure is called, the values are reset to their default condition, to prevent recursive traps from hanging the machine up, e.g. stack overflow in the stack overflow handling routine. Default error processing is explicitly undefined, but will usually be the lowest possible form of getting the error number to the outside world.

The TRP instruction generates an trap, the trap number being found on the stack. This is among other things useful for library routines, runtime systems etc.. Also it can be used by a low level error routine to pass the error to a higher level one (see example below).

The RTT instruction returns from the error routine and continues after the error. In the list below all errors marked with an asterisk ('\*') are considered to be fatal and it is explicitly undefined what happens if you try to restart after the error.

The way an error routine is called is completely compatible with normal calling conventions. The only way an error routine differs from normal procedures is the return. It has to use RTT instead of RET. This is necessary because all interpreter status is saved on the stack before calling the procedure and all this status has to be reloaded. Error numbers are in the range 0 to 255. There are three categories of error numbers:

- 0-63 EM-1 machine errors, e.g. illegal instruction.

- 64-127 Reserved for use by compilers, run time systems, etc.

- 128-255 Available for user programs.

EM-1 machine errors are numbered as follows:

- O\* Stack overflow

- 1\* Heap overflow

- 2\* Illegal instruction

- 3\* Illegal odd or zero argument

- 4\* Case error

- 5 Set bound error

- 6 Array bound error

- 7 Range bound error

- 8 Integer overflow

- 9 Double integer overflow

- 10 Floating overflow

- 11 Floating underflow

```

12

Divide by O

13

Divide by 0.0

Integer undefined

14

Double integer undefined

15

Floating undefined

16

17

Float -> int conversion error

Float -> double int conversion error

18

19

Double int -> int conversion error

20

Floating hardware error

21

Argument of LIN too high

22

Bad monitor call

23* CAL with wrong number of args

24

Bad argument of LAE

25* Addressing non existent memory

26* Bad pointer used

27* Procedure number too high

28* Program counter out of range

```

As an example, suppose a subroutine has to be written to generate random numbers. The usual method of doing this uses multiplications that can overflow without harm to the result of the procedure. This overflow should not be noticed by the user program since it has no idea whatsoever what happens inside the random procedure. This can be programmed as follows using the mechanism described above:

```

; This is the error number of integer overflow

let ovf err,8

save bss 4

; Room to save previous value of error routine

; Local procedure that must catch the overflow trap

pro catch, 2,0

; Load error number

lol O

; check for overflow

loc ovf err

; if other error call higher routine

bne 1

; load static link to random

lex 1

loc $catch

; load procedure number

; get ready to catch next overflow

siq

; return to random

rtt

; other error has occurred

; previous error routine

lde save

; other routine will get the traps now

sig

; remove the result of sig

beg -4

; stack error number

lol O

; call other error routine

; if other routine returns, do the same

trp

rtt

end

; entry point without parameters

pro random,0,1

; static link of catch will point to LB of random so all

lex O

; local variables of random are accessible from catch

loc $catch

; errors will be trapped to catch

sig

sde save

; save previous value

; calculate random number now, generating overflow at will

lde save

; restore previous status

```

.

#### 10. EM-1 MACHINE LANGUAGE

The EM-1 machine language is designed to make program text compact and to make decoding easy. Compact program text has many advantages: programs execute faster, programs occupy less primary and secondary storage and loading programs into satellite processors is faster. Since the decoding of EM-1 machine language is very simple, it is feasible to use interpreters as long as EM-1 hardware machines are not available. This chapter is irrelevant if back end compilers are used to produce executable target machine code.

#### 10.1. INSTRUCTION ENCODING

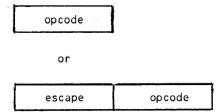

A design goal of EM-1 is to make the program text as compact as possible. Decoding must be easy, however. The encoding is fully byte oriented, without any small bit fields. There are 256 primary opcodes, one of which is an escape to a group of 256 secondary opcodes. EM-1 instructions without operands have a single opcode assigned, possibly escaped:

The situation for instructions with an operand is more complex. It is assumed that the machine words are two bytes long. There is always one opcode that takes the next two bytes as operand, high byte first (operands always fit in 16 bits):

| opcode | hibyte | lobyte |        |

|--------|--------|--------|--------|

| or     |        |        |        |

| escape | opcode | hibyte | lobyte |

For most instructions, however, some operand values predominate. The most frequent combinations of instruction and operand will be encoded in a single byte, called a mini:

opcode+operand (mini)

The savings for these mini opcodes are considerable, 66% to 75%. But the number of minis is restricted, since only 255 primary opcodes are available. Many instructions have the bulk of their operands fall in the range 0 to 255. Instructions that address global data have their operands distributed over a wider range, but small values of the high byte are very common. For all these cases there is another encoding that combines the instruction and the high byte of the operand into a single opcode. These opcodes are called shorties. Shorties may be escaped.

Escaped shorties are useless if the normal encoding has a primary opcode. Note that for some instruction-operand combinations three different encodings are available. It is the task of the assembler to select the shortest of these.

Further improvements are possible: many instructions have only even operands. If these operands are divided by two, then more of them will be encoded as shortie or mini. The operands of some other instructions, that give an object size in bytes, are even, except for the value 1. In this case the value 1 is encoded as 0, since 0 is not a valid size, and the other operand values are divided by two as above.

To reduce instruction length of most call instructions to one byte, a special mechanism is available. If all the instructions between a MRK and its corresponding CAL belong to a certain group (specified below), the assembler automatically replaces the MRK by the special instruction MRX. This redefines all the opcodes fetched until the CAL has executed. The redefined opcode table is called the "alternate context". Opcodes 0 up to (but excluding) CUTOFF have the same meaning as in the regular context. However, CUTOFF means call procedure 0, CUTOFF+1 means call procedure 1, etc. Instruction MRX may only be generated by the assembler, not by compilers.

It should now be clear that the instructions allowed between MRK and CAL in alternate context are just those with opcodes 0 to CUTOFF-1. When assigning opcodes to mnemonics, those useful in parameter passing have been given low values.

Assigning opcodes to instructions by the assembler is completely table driven. For details see appendix 2.

#### 10.2. LOAD FORMAT

The EM-1 machine language load format defines the interface between the EM-1 assembler/loader and the EM-1 machine itself. A load file consists of a header (16 words), the program text to be executed, a description of the global data area and the procedure descriptor table, in this order.

The header has two parts: the first half of it (8 words) aids in selecting the correct EM-1 machine or interpreter. Some EM-1 machines, for instance, may have hardware floating point instructions. The header words are used for:

- 0: magic number (07254)

- 1: flag bits with the following meaning:

- bitO: TEST; perform tests like integer overflow etc.

- bit1: PROFILE; for each source line: count the number of memory cycles executed.

- bit2: FLOW; for each source line: set a bit in a bitmap table if instructions on that line are executed.

- bit3: COUNT; for each source line: increment a counter if that line is entered.

- bit4: REALS; set if a program uses floating point instructions.

- bit5: EXTRA; more tests during compiler debugging.

- 2: number of unresolved references.

- 3: version number; used to detect obsolete EM-1 load files.

- 4: unused

- 5: unused

- 6: unused

- 7: unused

The second part of the header (8 words) describes the load file itself:

- 8: NTEXT; the program text size in bytes.

- 9: NDATA; the number of load file descriptors (see below).

- 10: NPROC; the number of entries in the procedure descriptor table.

- 11: ENTRY; procedure number of the procedure to start with.

- 12: NLINE; the maximum source line number.

- 13: unused

- 14: unused

- 15: unused

The program text consists of NTEXT bytes. NTEXT is always even. The first byte of the program text is the first byte of the instruction address space, i.e. it has address 0. The only pointers into the program text are found in the procedure descriptor table, so relocation is simple.

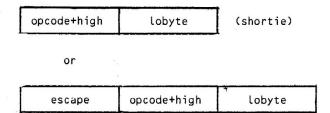

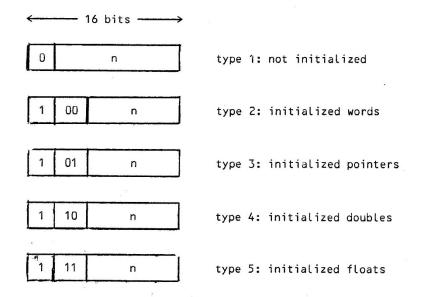

The global data area is described by the NDATA descriptors. Each descriptor describes a number of consecutive words. While reading the descriptors from the load file, one can initialize the global data area from low to high addresses. Five descriptor types are available, characterized by their first word:

- type 1: Reserve n words, not explicitly initialized (BSS and HOL).

- type 2: The next n words are initializers for the next n words of the global data area.

- type 3: The next n words of global data are initialized pointers into the EM-1 data address space. Interpreters that represent EM-1 pointers by true EM-1 addresses do not need this information, but interpreters that represent EM-1 pointers by target machine addresses must relocate all data pointers.

- type 4: The next 2\*n words of global data are initialized double precision integers. The load file contains n pairs of words as initializer. The first word of each pair is the most significant one.

- type 5: The load file contains n ASCII strings, null terminated, to initialize n floating point numbers in global data. Each string starts at a word boundary.

Note that the first descriptor describes the ABS block. This descriptor is of type 1.

The NPROC procedure descriptors on the load file consist of two words each: the first word gives the number of bytes for parameters, the second word gives the address of the first instruction of the procedure, assuming that program text starts at address 0.

#### 11.1. Introduction

An assembly language program consists of a series of lines, each containing 0 or 1 statements. A machine instruction may not be labeled. In other words, the label field on a machine instruction must be left blank. There are two kinds of labels, instruction and data labels. Labels start in column 1. Instruction labels are unsigned positive integers, and each must appear alone on a line by itself. The scope of an instruction label is its procedure.

The pseudoinstructions CON, ROM, and BSS may be labeled with a 1-8 character data label, the first character of which is a letter, period or underscore, followed by letters, digits, periods and underscores. Only 1 label per line is allowed. The use of the character "." followed by a number (e.g. .40) is recommended for compiler generated programs, since these are considered as a special case and handled more efficiently in compact assembly language (see below).

Each statement may contain an instruction mnemonic or pseudoinstruction. These must begin in column 2 or later (not column 1) and must be followed by a space, tab, semicolon or LF. Everything on the line following a semicolon is taken as a comment.

All constants are decimal unless started with a zero e.g. 0177, in which case they are octal. In CON and ROM pseudoinstructions, floating point numbers are distinguished by the presence of a decimal point or an exponent (indicated by E or e), or both. Double precision (long) integers are followed directly by an L or l.

Also allowed as initializers in CON and ROM are strings. Strings are surrounded by double quotes and may include  $\xxx$ , where  $\xxx$  is a 3-digit octal constant, e.g. CON "hello\012\000". Each string element initializes a single byte. Strings are padded at the end up to a multiple of the word size.

Local labels are referred to as \*1, \*2, etc. in CON and ROM pseudoin-structions (to distinguish them from constants), but without the asterisk in branch instructions, e.g. BRF 3, not BRF \*3.

The notation procname is used to mean the descriptor number for the procedure with the specified name.

An input file may contain many procedures. A procedure consists of zero or more pseudoinstructions, a PRC statement, a (possibly empty) collection of instructions and pseudoinstructions and finally an END statement. The very last statement on the input file must be EOF. The END directly preceding the EOF may be omitted.

Input to the assembler is in lower case, if available. Upper case is used in this document merely to distinguish key words from the surrounding prose.

#### 11.2. Pseudo instructions

First the notation used for the operands of the pseudo instructions.

<num> = an integer constant

<sym> = an identifier

<arg> = <num> or <sym>

<val> = <arg>, long constant (ending with L or l), real constant, string

constant (surrounded by double quotes), procedure number (starting

with \$) or instruction label (starting with \*).

<...>\* = zero or more of <...>

<...>+ = one or more of <...>

Four pseudo instructions request global data:

BSS <num>

Reserve <num> bytes, not explicitly initialized. <num> must be a multiple of the word size.

HOL <num>

Idem, but all following absolute global data references will refer to this block.

CON <val>+

Assemble global data words initialized with the <val> constants.

ROM <val>+

Idem, but the initialized data will never be changed.

Three pseudo instructions partition the input into procedures:

PRO <sym>,<num1>,<num2>

Start of procedure.  $\langle sym \rangle$  is the procedure name.  $\langle num1 \rangle$  is the number of bytes for arguments.  $\langle num2 \rangle$  is 1 for procedure names to be exported out of the current module, 0 otherwise.

END

End of Procedure.

E OF

End of module.

Besides the export flag in PRO, six other pseudo instructions are involved with separate compilation and linking:

EXD <sym>

Export data. <sym> is exported out of this module.

IMA <sym>

Import address. IMA allows global symbol <sym> to be used before it is

defined. Note that <sym> may be defined in the same module.

IMC <sym>

Similar to IMA, but used for imported single word constants. These two different forms are necessary, because the assembler must know how much storage must be allocated if <sym> is used in CON or ROM.

FWA <sym>

Forward address. Notify the assembler that <sym> will be defined later on in this module, so that it may be used before being defined.

FWC <sym>

Similar to FWA, but for constants.

FWP <sym>

Forward procedure reference. FWP allows <sym> to be used before it is defined. <sym> must be defined in the same module and must not be exported. Normally, unknown procedure names are entered in the undefined global reference table, so that their names will be known outside this module. Procedure names introduced by FWP are treated differently, however, to prevent their being exported.

Three other pseudo instructions provide miscellaneous features:

LET <sym>,<arg>

Assembly time assignment of the second operand to the first one.

EXC <num1>,<num2>

Two blocks of instructions preceding this one are interchanged before being assembled. <num1> gives the number of lines of the first block. <num2> gives the number of lines of the second one. Blank and pure comment lines do not count.

MES <num>, <val>\*

A special type of comment. Used by compilers to communicate with the optimizer, assembler, etc. as follows:

MES 0 -

An error has occurred, stop assembly.

MES 1 ~

Suppress optimization

MES 2 -

Use virtual memory (EM-2)

MES 3,<num1>,<num2> -

Indicates that a local variable is never referenced indirectly. <num1> is offset in bytes from LB. <num2> indicates the class of the variable.

MES 4 -

Number of source lines (for profiler).

MES 5 -

Floating point used.

MES 6, <val>\* -

${\tt Comment.}$  Used to provide comments in compact assembly language (see below).

Each back end is free to skip irrelevant MES pseudos.

#### 11.3. The Compact Assembly Language

The assembler accepts input in a highly encoded form. This form is intended to reduce the amount of file transport between the compiler and assembler, and also reduce the amount of storage required for storing libraries. Libraries are stored as archived compact assembly language, not machine language. The compact assembly language assumes that a machine word is two bytes long.

When beginning to read the input, the assembler is in neutral state, and expects either a label or an instruction (including the pseudoinstructions). The meaning of the next byte(s) when in neutral state is as follows, where b1, b2 etc. represent the succeeding bytes.

```

G Reserved for future use

1-139 Machine instructions, see Appendix 2, alphabetical list

140-149 Reserved for future use

150-165 BSS,CON,END,EOF,EXC,EXD,FWA,FWC,FWP,HOL,IMA,IMC,LET,MES,PRO,ROM

166-179 Reserved for future pseudoinstructions

180-239 Local labels 0 - 59 (180 is local label 0 etc.)

240-244 See the Common Table below

245-255 Not used

```

After a label, the assembler is back in neutral state; it can immediately accept another label or an instruction in the very next byte. There are no linefeeds used to separate lines.

If an opcode has no operands, the assembler is back in neutral state after reading the one byte containing the instruction number. If it has one or more operands (only pseudos have more than 1), the operands follow directly, encoded as follows:

```

O-239 Integer constant from O to 239 240-255 See the Common Table below

```

#### Common Table for Neutral State and Operands

| 240 b1                        | Local label b1 (Not used for branches)                                                      |

|-------------------------------|---------------------------------------------------------------------------------------------|

| 241 b1 b2                     | 16 bit local label (256*b2 + b1)                                                            |

| 242 b1                        | Global label .O255, with b1 being the label                                                 |

| 243 b1 b2                     | Global label .065535 with 256*b2+b1 being the label                                         |

| 244 <ascii string=""></ascii> | Global symbol not of the form .nnn                                                          |

| 245 <ascii string=""></ascii> | Procedure name (not including \$)                                                           |

| 246 <ascii string=""></ascii> | String used in CON or ROM (no quotes)                                                       |

| 247 <ascii string=""></ascii> | Real value for CON                                                                          |

| 248 constant 0-255            | (In fact only used for 241-255 in practice)                                                 |

| 249 b1                        | <pre><negative -1="" -255="" b1="" constant="" in="" of="" range="" to=""></negative></pre> |

| 250 b1 b2                     | (16 bit constant) 256*b2+b1                                                                 |

251 <ASCII string> Double precision integer constant

255 Delimiter for CON, ROM lists

The notation <ASCII string> consists first of a length field, and then an arbitrary string of bytes. If the length field starts out with 0-254, that is the length of the string. If it is 255, the length follows in the next two bytes, low order byte first.

The pseudoinstructions fall into several categories, depending on their operands:

```

Group 1 -- END, EOF have no operands

Group 2 -- BSS, EXC, HOL have a known number of numeric operands

Group 3 -- EXD, FWA, FWC, FWP, IMA, IMC, LET, PRO start with a string

Group 4 -- CON, MES, ROM have a variable number of various things

```

Group 1 is easy; just go back into neutral state immediately. Groups 2 and 3 use the encoding described above. Group 4 also uses the encoding listed above, with a 255 byte after the last operand to indicate the end of the list.

```

Example ASCII

Example compact

(LOC = 76, BRF = 18 here):

2

182

1

181

LOC 10

76 10

LOC -10

LOC 300

76 249 10

76 250 44 1

BRF 19

18 19

300

241 44 1

242 3 152 4 9 240 2 245 3 102 111 111 255

.3 CON 4,9,*2,$foo

LOC .35

76 242 35

```

#### 12. ASSEMBLY LANGUAGE INSTRUCTION LIST

For each instruction in the list the range of operand values in the assembly language is given. These ranges are all subranges of -32768..32767 and are indicated by letters:

```

m: full range, i.e. -32768..32767

n: 0..32767

x: 0..32766 and even

y: 1 or (2..32766 and even)

z: -32768..32766 and even

p: 2..32766 and even

r: 0, 1 or 2

```

The letters should not be confused with the letters used in the EM-1 instruction table in appendix 2. Instructions that check for undefined operands and underflow or overflow are indicated by (\*).

```

GROUP 1: LOAD

LOC m - Load constant (i.e. push it onto the stack)

LNC m - Load negative constant

LOL x - Load local word x

LOE x - Load external word x

LOP'x - Load word pointed to by x-th local

LAI y - Load auto increment y bytes (address of pointer on stack)

LOF m - Load offsetted. (top of stack + m yield address)

LAL x - Load address of local

LAE x - Load address of external